|

embedded-software

reusable software modules for embedded systems

|

|

embedded-software

reusable software modules for embedded systems

|

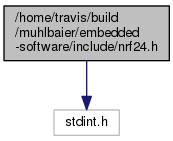

#include <stdint.h>

Go to the source code of this file.

Data Structures | |

| struct | nrf24_radio_t |

| struct | nrf24_radio_t::settings |

Macros | |

| #define | nRF24_ISR(nrf_object) Task_Queue( (task_t)nRF24_EventHandler, nrf_object) |

| #define | CONFIG 0x00 |

| #define | EN_AA 0x01 |

| #define | EN_RXADDR 0x02 |

| #define | SETUP_AW 0x03 |

| #define | SETUP_RETR 0x04 |

| #define | RF_CH 0x05 |

| #define | RF_SETUP 0x06 |

| #define | STATUS 0x07 |

| #define | OBSERVE_TX 0x08 |

| #define | CD 0x09 |

| #define | RX_ADDR_P0 0x0A |

| #define | RX_ADDR_P1 0x0B |

| #define | RX_ADDR_P2 0x0C |

| #define | RX_ADDR_P3 0x0D |

| #define | RX_ADDR_P4 0x0E |

| #define | RX_ADDR_P5 0x0F |

| #define | TX_ADDR 0x10 |

| #define | RX_PW_P0 0x11 |

| #define | RX_PW_P1 0x12 |

| #define | RX_PW_P2 0x13 |

| #define | RX_PW_P3 0x14 |

| #define | RX_PW_P4 0x15 |

| #define | RX_PW_P5 0x16 |

| #define | FIFO_STATUS 0x17 |

| #define | DYNPD 0x1C |

| #define | FEATURE 0x1D |

| #define | RX_ADDR_BASE RX_ADDR_P0 |

| #define | AW_5B 0x03 |

| #define | AW_4B 0x02 |

| #define | AW_3B 0x01 |

| #define | MASK_RX_DR 0x40 |

| #define | MASK_TX_DS 0x20 |

| #define | MASK_MAX_RT 0x10 |

| #define | EN_CRC 0x08 |

| #define | CRCO 0x04 |

| #define | PWR_UP 0x02 |

| #define | PRIM_RX 0x01 |

| #define | ENAA_P5 0x20 |

| #define | ENAA_P4 0x10 |

| #define | ENAA_P3 0x08 |

| #define | ENAA_P2 0x04 |

| #define | ENAA_P1 0x02 |

| #define | ENAA_P0 0x01 |

| #define | ERX_P5 0x20 |

| #define | ERX_P4 0x10 |

| #define | ERX_P3 0x08 |

| #define | ERX_P2 0x04 |

| #define | ERX_P1 0x02 |

| #define | ERX_P0 0x01 |

| #define | AW 0x01 |

| #define | ARD 0x10 |

| #define | ARC 0x01 |

| #define | CONT_WAVE 0x80 |

| #define | RF_DR_LOW 0x20 |

| #define | PLL_LOCK 0x10 |

| #define | RF_DR_HIGH 0x08 |

| #define | RF_PA_HIGH 0x04 |

| #define | RF_PA_LOW 0x02 |

| #define | RX_DR 0x40 |

| #define | TX_DS 0x20 |

| #define | MAX_RT 0x10 |

| #define | RX_P_NO 0x02 |

| #define | TX_FULL 0x01 |

| #define | PLOS_CNT 0x10 |

| #define | ARC_CNT 0x01 |

| #define | TX_REUSE 0x40 |

| #define | TX_FULL_FIFO 0x20 |

| #define | TX_EMPTY 0x10 |

| #define | RX_FULL 0x02 |

| #define | RX_EMPTY 0x01 |

| #define | DPL_P5 0x20 |

| #define | DPL_P4 0x10 |

| #define | DPL_P3 0x08 |

| #define | DPL_P2 0x04 |

| #define | DPL_P1 0x02 |

| #define | DPL_P0 0x01 |

| #define | EN_DPL 0x04 |

| #define | EN_ACK_PAY 0x02 |

| #define | EN_DYN_ACK 0x01 |

| #define | REGISTER_MASK 0x1F |

| #define | R_REGISTER 0x00 |

| #define | W_REGISTER 0x20 |

| #define | R_RX_PAYLOAD 0x61 |

| #define | W_TX_PAYLOAD 0xA0 |

| #define | FLUSH_TX 0xE1 |

| #define | FLUSH_RX 0xE2 |

| #define | REUSE_TX_PL 0xE3 |

| #define | ACTIVATE 0x50 |

| #define | R_RX_PL_WID 0x60 |

| #define | W_ACK_PAYLOAD 0xA8 |

| #define | W_TX_PAYLOAD_NO_ACK 0xB0 |

| #define | NOP 0xFF |

Typedefs | |

| typedef struct nrf24_radio_t | nrf24_t |

Enumerations | |

| enum | nrf24_pa_level_e { NRF24_PA_LOW = 0, NRF24_PA_MID, NRF24_PA_HIGH, NRF24_PA_MAX } |

| enum | nrf24_datarate_e { NRF24_250KBPS = 0, NRF24_1MBPS, NRF24_2MBPS } |

| enum | nrf24_crc_mode_e { NRF24_NO_CRC = 0, NRF24_CRC_8BIT, NRF24_CRC_16BIT } |

Functions | |

| void | nRF24_Init (nrf24_t *nrf_object) |

| void | nRF24_OpenRxPipe (nrf24_t *nrf_object, uint8_t pipenum, uint64_t address) |

| void | nRF24_OpenTxPipe (nrf24_t *nrf_object, uint64_t address) |

| void | nRF24_EventHandler (nrf24_t *nrf_object) |

| void | nRF24_StartListening (nrf24_t *nrf_object) |

| void | nRF24_Standby (nrf24_t *nrf_object) |

| void | nRF24_WriteReg (nrf24_t *nrf_object, uint8_t reg_address, uint8_t value) |

| void | nRF24_WriteMultReg (nrf24_t *nrf_object, uint8_t reg_address, uint8_t *data_ptr, uint8_t length) |

| uint8_t | nRF24_ReadReg (nrf24_t *nrf_object, uint8_t reg_address) |

| uint8_t | nRF24_GetPayloadLength (nrf24_t *nrf_object) |

| void | nRF24_Write (nrf24_t *nrf_object, uint8_t *buf, uint8_t length) |

| void | nRF24_Read (nrf24_t *nrf_object, uint8_t *buf, uint8_t length) |

| void | nRF24_WriteAck (nrf24_t *nrf_object, uint8_t *buf, uint8_t length, uint8_t pipe) |

| void | nRF24_SetPowerAmplificationLevel (nrf24_t *nrf_object, nrf24_pa_level_e level) |

| void | nRF24_SetDataRate (nrf24_t *nrf_object, nrf24_datarate_e rate) |

| void | nRF24_SetCRCMode (nrf24_t *nrf_object, nrf24_crc_mode_e mode) |

| void | nRF24_SetChannel (nrf24_t *nrf_object, uint8_t channel) |

| void | nRF24_SetActive (nrf24_t *nrf_object, uint8_t active) |

| void | nRF24_SetRetries (nrf24_t *nrf_object, uint8_t delay, uint8_t count) |

| void | nRF24_FlushRx (nrf24_t *nrf_object) |

| void | nRF24_FlushTx (nrf24_t *nrf_object) |

| #define ACTIVATE 0x50 |

| #define ARC 0x01 |

| #define ARC_CNT 0x01 |

| #define ARD 0x10 |

| #define AW 0x01 |

| #define AW_3B 0x01 |

| #define AW_4B 0x02 |

| #define AW_5B 0x03 |

| #define CD 0x09 |

| #define CONFIG 0x00 |

| #define CONT_WAVE 0x80 |

| #define CRCO 0x04 |

| #define DPL_P0 0x01 |

| #define DPL_P1 0x02 |

| #define DPL_P2 0x04 |

| #define DPL_P3 0x08 |

| #define DPL_P4 0x10 |

| #define DPL_P5 0x20 |

| #define DYNPD 0x1C |

| #define EN_AA 0x01 |

| #define EN_ACK_PAY 0x02 |

| #define EN_CRC 0x08 |

| #define EN_DPL 0x04 |

| #define EN_DYN_ACK 0x01 |

| #define EN_RXADDR 0x02 |

| #define ENAA_P0 0x01 |

| #define ENAA_P1 0x02 |

| #define ENAA_P2 0x04 |

| #define ENAA_P3 0x08 |

| #define ENAA_P4 0x10 |

| #define ENAA_P5 0x20 |

| #define ERX_P0 0x01 |

| #define ERX_P1 0x02 |

| #define ERX_P2 0x04 |

| #define ERX_P3 0x08 |

| #define ERX_P4 0x10 |

| #define ERX_P5 0x20 |

| #define FEATURE 0x1D |

| #define FIFO_STATUS 0x17 |

| #define FLUSH_RX 0xE2 |

| #define FLUSH_TX 0xE1 |

| #define MASK_MAX_RT 0x10 |

| #define MASK_RX_DR 0x40 |

| #define MASK_TX_DS 0x20 |

| #define MAX_RT 0x10 |

| #define NOP 0xFF |

| #define OBSERVE_TX 0x08 |

| #define PLL_LOCK 0x10 |

| #define PLOS_CNT 0x10 |

| #define PRIM_RX 0x01 |

| #define PWR_UP 0x02 |

| #define R_REGISTER 0x00 |

| #define R_RX_PAYLOAD 0x61 |

| #define R_RX_PL_WID 0x60 |

| #define REGISTER_MASK 0x1F |

| #define REUSE_TX_PL 0xE3 |

| #define RF_CH 0x05 |

| #define RF_DR_HIGH 0x08 |

| #define RF_DR_LOW 0x20 |

| #define RF_PA_HIGH 0x04 |

| #define RF_PA_LOW 0x02 |

| #define RF_SETUP 0x06 |

| #define RX_ADDR_BASE RX_ADDR_P0 |

| #define RX_ADDR_P0 0x0A |

| #define RX_ADDR_P1 0x0B |

| #define RX_ADDR_P2 0x0C |

| #define RX_ADDR_P3 0x0D |

| #define RX_ADDR_P4 0x0E |

| #define RX_ADDR_P5 0x0F |

| #define RX_DR 0x40 |

| #define RX_EMPTY 0x01 |

| #define RX_FULL 0x02 |

| #define RX_P_NO 0x02 |

| #define RX_PW_P0 0x11 |

| #define RX_PW_P1 0x12 |

| #define RX_PW_P2 0x13 |

| #define RX_PW_P3 0x14 |

| #define RX_PW_P4 0x15 |

| #define RX_PW_P5 0x16 |

| #define SETUP_AW 0x03 |

| #define SETUP_RETR 0x04 |

| #define STATUS 0x07 |

| #define TX_ADDR 0x10 |

| #define TX_DS 0x20 |

| #define TX_EMPTY 0x10 |

| #define TX_FULL 0x01 |

| #define TX_FULL_FIFO 0x20 |

| #define TX_REUSE 0x40 |

| #define W_ACK_PAYLOAD 0xA8 |

| #define W_REGISTER 0x20 |

| #define W_TX_PAYLOAD 0xA0 |

| #define W_TX_PAYLOAD_NO_ACK 0xB0 |